TriCore: Architecture

说明

本文是 英飞凌 架构文档 TriCore TC162P core archiecture Volume 1 of 2 (infineon.com) 的笔记,稍作整理方便查阅,错误之处,还请指正,谢谢 :)

1. Architecture

2. General Purpose & System Register

名词列表:

类型 | 简称 | 全称 | 说明 |

名词缩写 | GPR | General Purpose Register | 通用寄存器 |

名词缩写 | CSFR | Core Special Function Register | 核寄存器 |

寄存器 | SP | Stack Pointer | 栈指针 |

寄存器 | PC | Program Counter | |

名词缩写 | RA | Return Address | |

寄存器 | PSW | Program Status Word Register | |

寄存器 | PCXI | Previous Context Information and Pointer Register | |

名词缩写 | ISP | Interrupt Stack Pointer | |

名词缩写 | CSA | Context Save Area | |

名词缩写 | FCX | Free Context List | |

寄存器 | FCX | Free CSA List Head Pointer Register | |

寄存器 | LCX | Free CSA List Limit Pointer Register | |

名词缩写 | PCX | Previous Context Area | |

寄存器 | PCX | Previous Context Pointer Register | |

| 名词缩写 | SMT | Software Managed Tasks | |

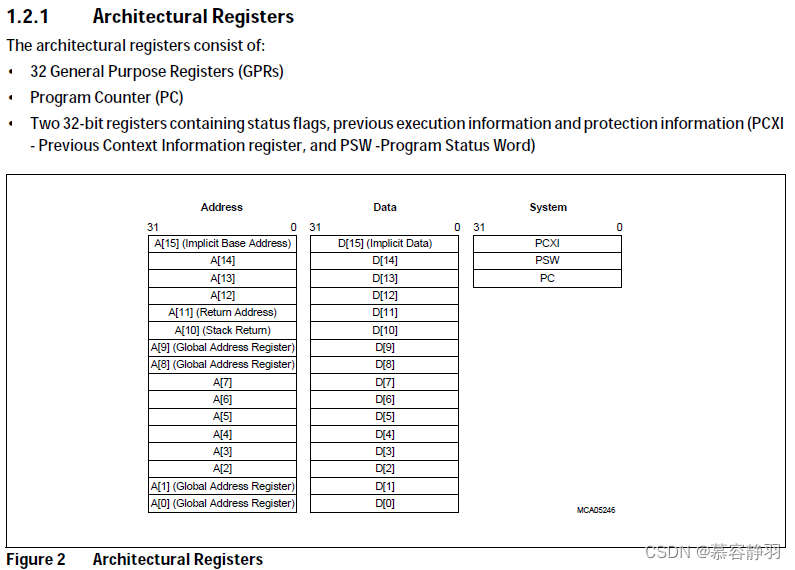

2 种核心寄存器:

- GPR(General Purpose Register)

- 16 DATA Register(DGPRs):D[0]~D[15];

- 16 ADDRESS Register(AGPRs): A[0]~A[15];

- CSFR(Core Special Function Register):控制核的操作,提供核的状态。

寄存器种类概览:

- • General Purpose Registers

- • System registers (PSW, PC, PCXI)

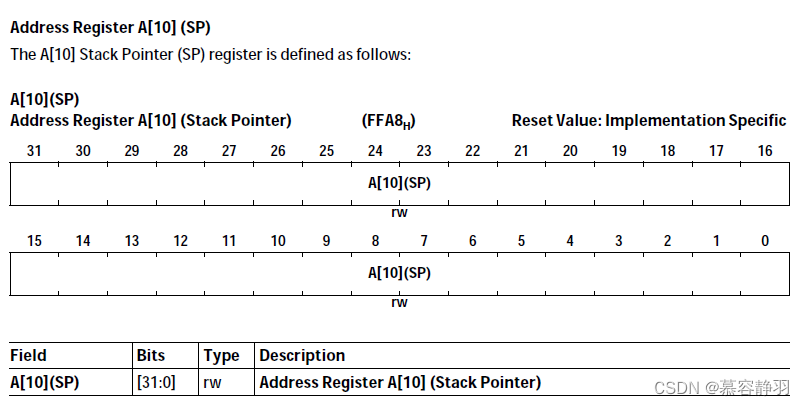

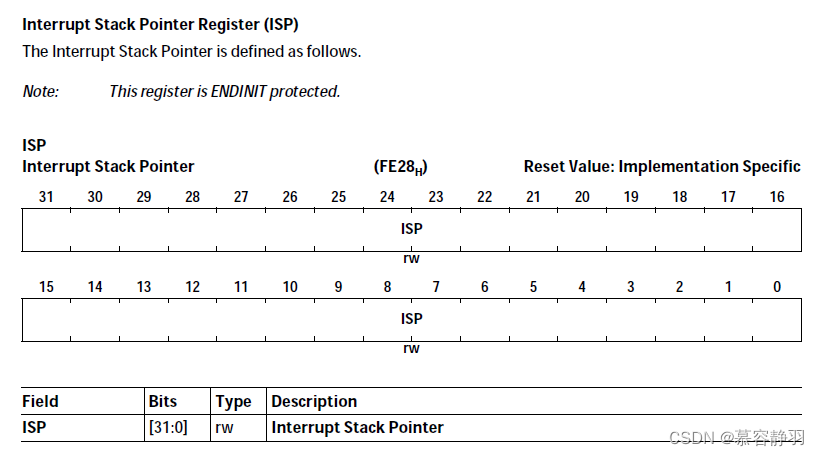

- • Stack Management registers are (A[10] and ISP)

- • SYSCON and CPU_ID registers

- • Trap registers

- • Context Management registers

- • Memory Protection registers

- • Memory Management registers

- • Debug registers

- • Floating Point registers

- • Special Function registers associated with the core

ENDINIT Protection

TriCore 架构支持操作状态(operational state)之前的初始化状态(initialisation state)的概念。

当处于初始化状态时,可以使用 MTCR 指令修改所有CSFR。

在操作状态下,只有一部分CSFR可以通过这种方式进行修改。所有其他功能在这些状态之间保持相同。

仅在初始化状态下可写入(修改)的 CSFR 被描述为受 ENDINIT 保护。

初始化状态和操作状态之间的转换由系统实现控制。该设备工具只允许在初始化状态下更改关键 CSFR,从而为关键 CSFR 增加了额外的保护级别。

以下寄存器受 ENDINIT 保护:

• BTV、BIV、ISP、PMA0、PMA1、PMA2、PCON0、DCON0、SEGEN

还提供了安全版本的 ENDINIT 保护。 以下寄存器受 SAFETY_ENDINIT 保护:

• SMACON、SYSCON、COMPAT、TPS_EXTIM_ENTRY_LVAL、TPS_EXTIM_EXIT_LVAL

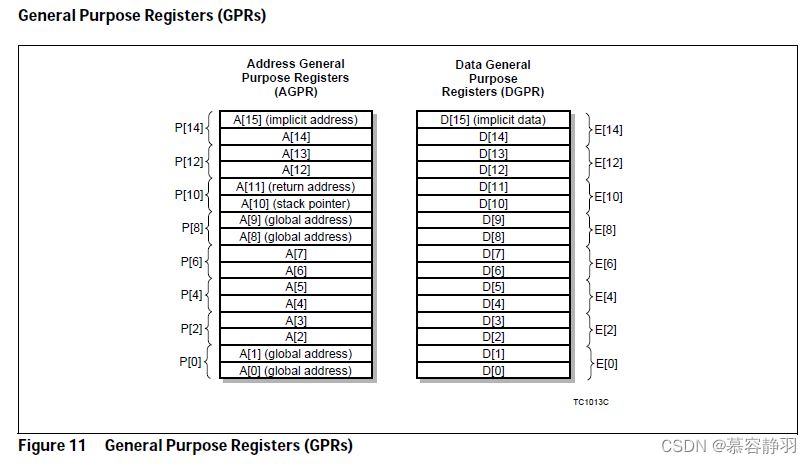

GPRs

- GPR(General Purpose Register)包括:

- 16 DATA Register(DGPRs):D[0]~D[15];

- 16 ADDRESS Register(AGPRs): A[0]~A[15];

数据和地址寄存器的分离可以提高算术和内存操作的并行执行效率。几个指令允许在数据和地址寄存器之间交换信息(例如,用于创建或派生表索引)。两个连续的奇-偶数据寄存器可以串联形成八个扩展大小寄存器(E[0]、E[2]、E[4]、E[6]、E[8]、E[10]、E[ 12] 和 E[14]) 从而支持 64 位值。 地址寄存器(P[0]、P[2]、P[4]、P[6]、P[8]、P[10]、P[12] 和 P[14])可以以同样的方法方式。

GPR进一步分类:

- 寄存器 A[0]、A[1]、A[8] 和 A[9] 被定义为系统全局寄存器。它们的内容不会在调用、陷阱或中断中保存或恢复;

- A[10] 用作栈指针 (SP,Stack Pointer);

- A[11] 用于:

- 存储函数调用(calls)和链接跳转(linked jumps)的返回地址 (RA,Return Address);

- 存储中断(Interrupt)和陷阱(Trap)的返回程序计数器 (PC,Program Counter) 值。

- 虽然 32 位指令可以无限使用 GPR,但许多 16 位指令隐含地使用 A[15] 作为它们的地址寄存器和 D[15] 作为它们的数据寄存器。这种隐式使用简化了将这些指令编码为 16 位的过程。

- 使用奇数/偶数寄存器对可支持 64 位数据值。在汇编语法中,这些寄存器对被称为 一对32 位寄存器(例如,D[9]/D[8])或扩展的 64 位寄存器。例如,E[8] 是 D[9] 和 D[8] 的串联,其中 D[8] 是 E[8] 的最低有效字。为了支持扩展寻址模式,偶数/奇数地址寄存器对将扩展地址引用保存为一对 32 位地址寄存器(例如 A[8]/A[9])。

- 没有单独的浮点寄存器。数据寄存器用于执行浮点运算。

- 使用快速上下文切换支持自动保存和恢复浮点数据。

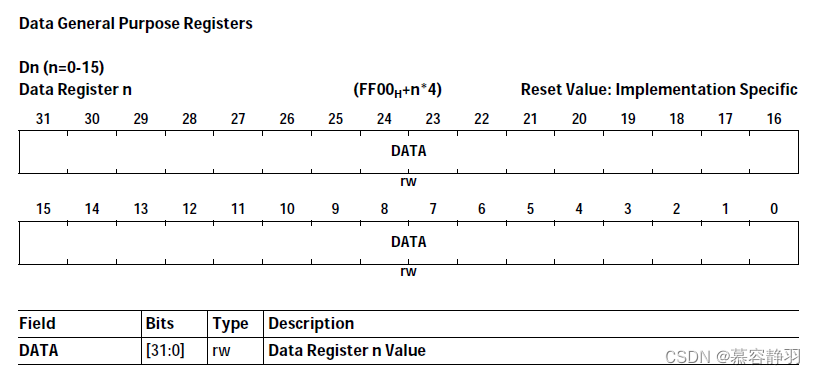

32bit 数据寄存器

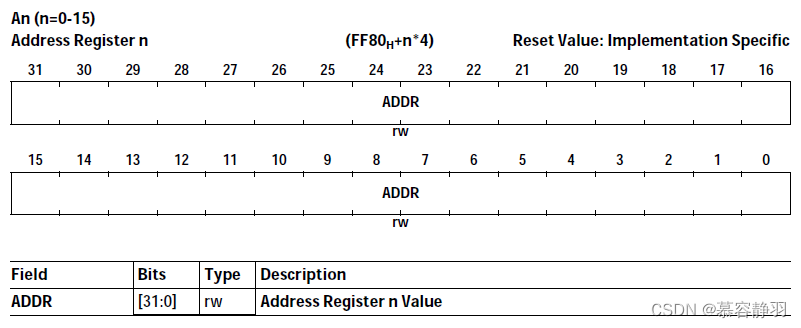

32bit地址寄存器

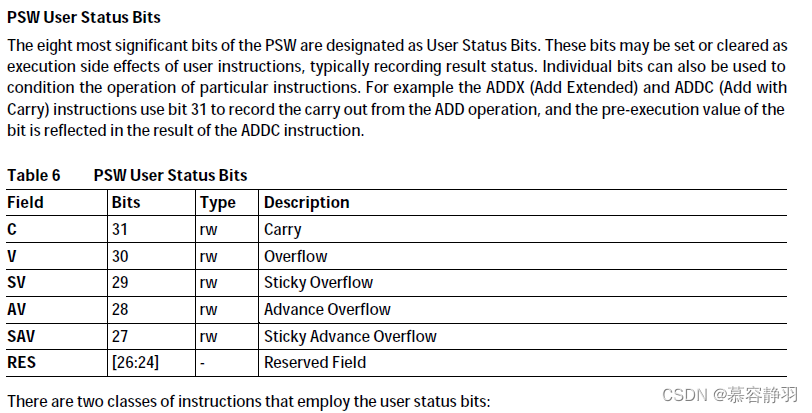

Program State Information Registers

以下3个寄存器包含程序状态信息:

- PC: Program Counter

- PSW: Program Status Word

- PCXI: Previous Context Information

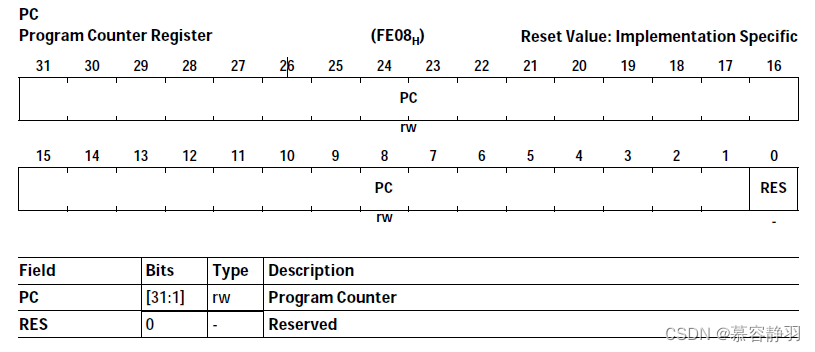

PC

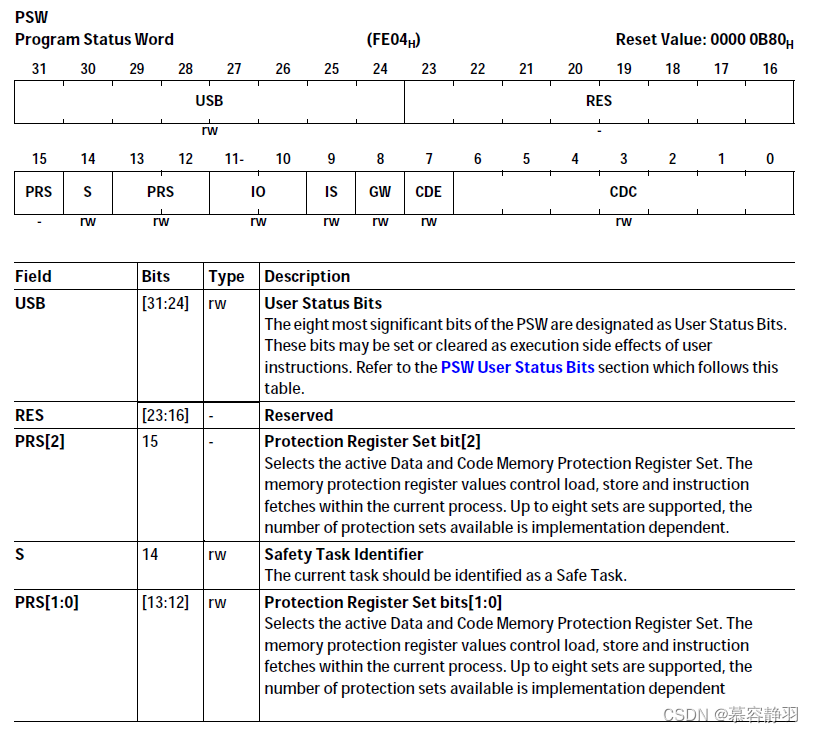

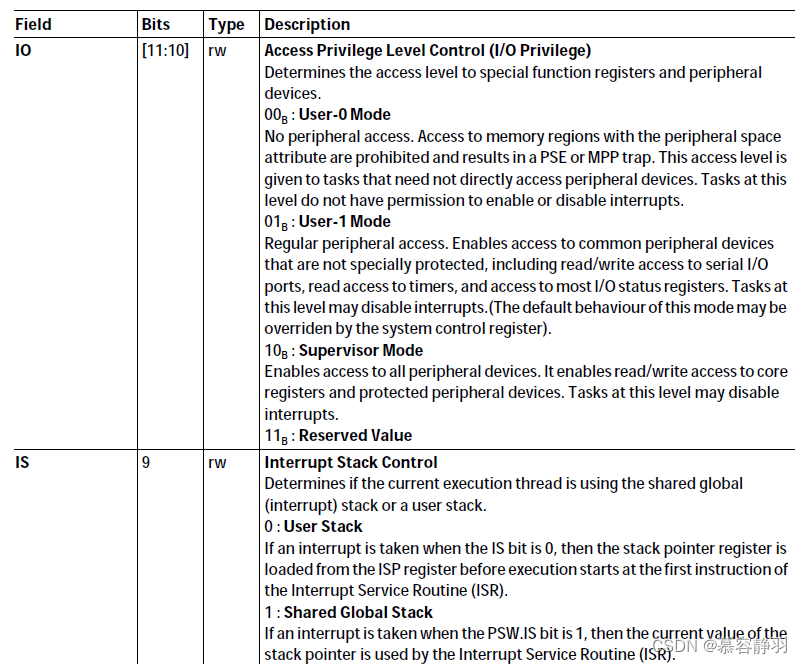

PSW

Access Privilege Level Control (I/O Privilege)

Interrupt Service Routines (ISRs) are dispatched by hardware in response to an interrupt. An ISR is the code that is invoked directly by the processor on receipt of an interrupt.

- User-0 Mode: Used for tasks that do not access peripheral devices. This mode may not enable or disable interrupts.

- User-1 Mode: Used for tasks that access common, unprotected peripherals. Typically this would be a read or write access to serial port, a read access to timer, and most I/O status registers. Tasks in thismodemaydisable interrupts. (The default behaviour of this mode may be overriden by the system control register).

- Supervisor Mode: Permits read/write access to system registers and all peripheral devices. Tasks in this mode may disable interrupts.

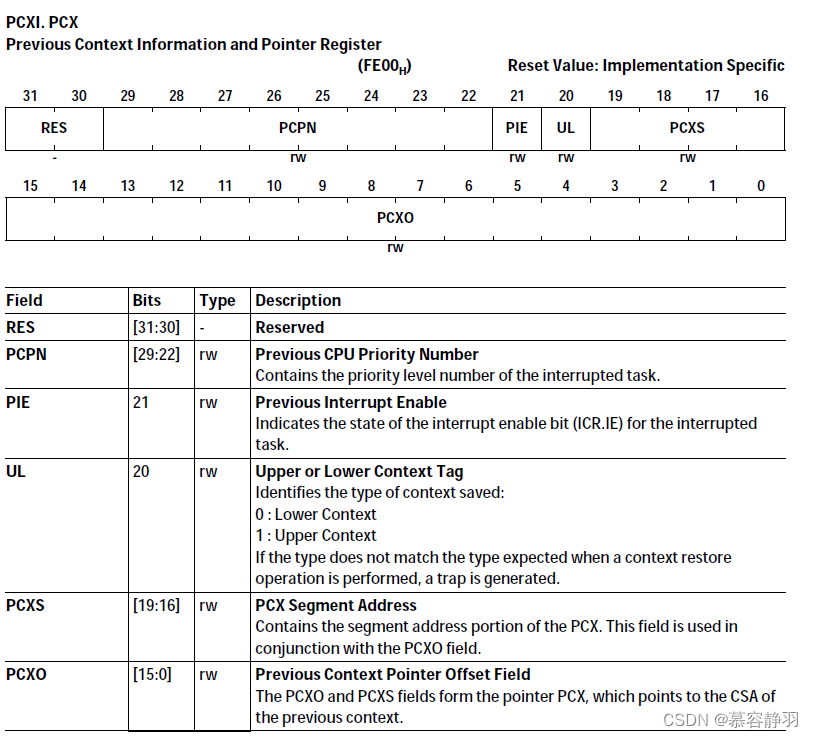

PCXI

什么是 Context:

处理器用作定义任务的状态的所有相关元素称之为 Context,使用这些元素任务能够继续执行。

这些元素包括:PC,PCXI 和 PSW。

TriCore架构通过硬件有效地管理和维护任务的上下文。

Stack Management Registers

TriCore架构中的栈管理支持用户栈(User Stack)和中断栈(Interrupt Stack)。地址寄存器 A[10]、中断栈指针 (ISP) 和一个 PSW 位用于栈管理。

A[10] 用作栈指针。该寄存器的初始内容通常由 RTOS 在创建任务时设置,这允许将私有栈区域分配给各个任务。

ISP 有助于防止中断服务程序 (ISR) 访问私有栈区域并可能干扰软件管理任务的上下文。Tricore结构实现了使用 ISP 而不是私有栈指针的自动切换。

PSW.IS 位指示哪个栈指针有效。

当发生中断并且被中断的任务正在使用其私有堆栈(PSW.IS == 0)时,SP的内容和被中断任务的UCX一起被保存,A[10](SP) 加载 ISP 的当前内容。

当发生中断或陷阱并且被中断的任务已经在使用中断栈(PSW.IS == 1)时,则不执行 A[10](SP) 的预加载。中断服务程序 (ISR) 在中断程序离开的位置继续使用中断栈。

通常只需要在初始化例程期间初始化 ISP 一次。但是,根据应用需要,可以在执行期间修改 ISP。请注意,没有什么可以阻止 ISR 或系统服务例程在私有栈上执行。

3. Task and Function

Context

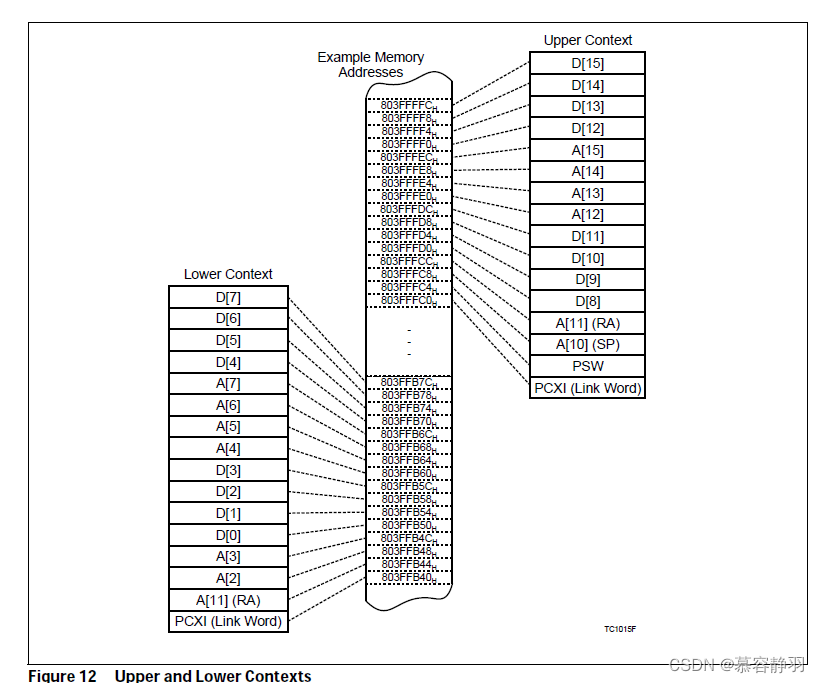

CSA 包括2类:

Upper Context (上文,简称 UCX)包括:

- 高位地址寄存器A[10]~A [15];

- 高位数据寄存器 D[8]~D[15];

- PCXI 和 PSW;

- 出于函数调用的目的,这些寄存器被指定为非易失性(它们的内容在调用过程中被保留)

Lower Context (下文,简称 LCX)包括:

- 低位地址寄存器A[2]~A [7];

- 低位数据寄存器 D[0]~D[7];

- PCXI 和 A[11](Return Address);

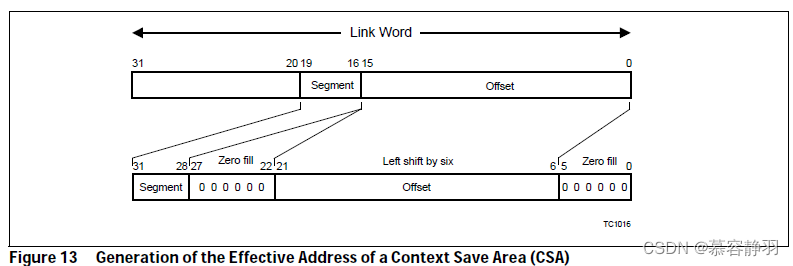

CSAs(Context Save Areas):

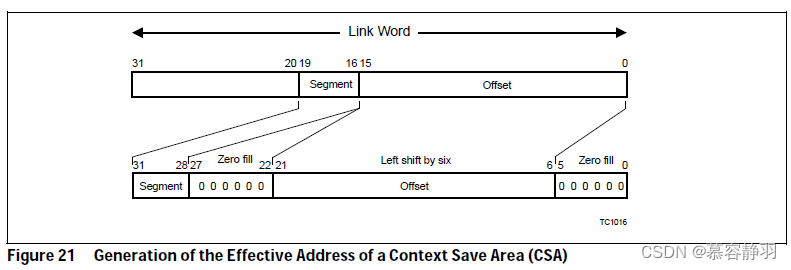

保存UCX或LCX的存储区称之为 CSA。Context 在保存到内存中时占用16 words(64 bytes)。每个CSA用作保存UCX或LCX,CSA之间使用 Link Word (PCXI)链接,组成一个链表。Link Word(后面简称LW) 结构上分2 部分,4bit 的 segment 和16bit 的offset,两部分合并起来产生EA(Effective Address),具体过程见下图(LinkWord 中保存的就是PCXI 寄存器的值):

每个地址段内的总的CSA可用范围是4MBytes,因此最多可以保存 2^16 (65535)个CSA。

Context Switching Operation

RET:Return From Call

REF:Return From Exception

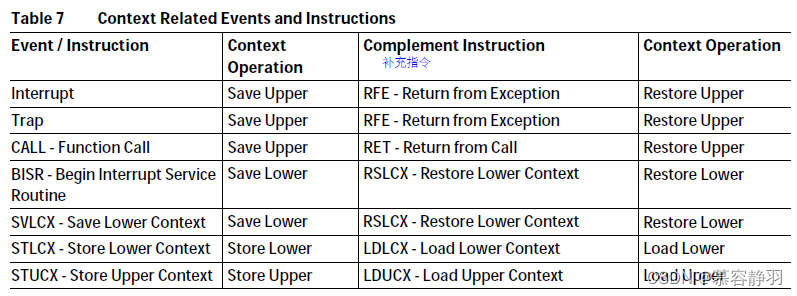

当上面 Table 7 中的 Event/Instruction 发生时就会 switch task(切换任务)。

当发生 External Interrupt、Trap、Function Call (外部中断,陷阱或函数调用)的时候(硬件)会自动保存UCX,LCX 则要通过明确的(人为软件)指令进行保存。Table7 中操作说明:

序号 | operation | explaination | Converse(逆向操作) |

1 | Save | “保存”是从链接字中读取 FCX 的下一个值之后,通过空闲 CSA 列表头指针寄存器 (FCX) 进行的存储。 ‘Save’ is a store through the Free CSA List Head Pointer register (FCX) after the next value for the FCX is read from the Link Word. | Restore |

2 | Store | ‘Store’是通过指令的有效地址(EA)进行存储,不改变 CSA 列表或 FCX 寄存器。 ‘Store’ is a store through the Effective Address of the instruction with no change to the CSA list or the FCX register. | Load |

就对内容的维护方式而言,UCX 和 LCX对寄存器的处理存在本质区别。LCX 的寄存器类似于全局寄存器,中断处理程序(Interrupt handler)、陷阱处理程序(Trap Handler)或被调用函数(Called Function)看到的值与中断、陷阱或发生调用前寄存器中的值相同。在中断内、陷阱处理程序内或调用函数内对这些寄存器所做的任何更改在返回后仍然存在,因为调用 RET (适用于 CALL) 或 RFE (适用于 Interrupt+Trap) 指令不会自动恢复(restore)他们。这意味着:

- 对于函数调用: LCX 寄存器可用于将参数传递给被调用的函数并从这些函数中传递返回值出来;

- 对于interrupt 和 trap,Interrupt handler 和 trap handler 必须在使用这些寄存器之前保存(save)其原始值,并在退出之前恢复(restore)原始值。

UCX 寄存器不保证是静态硬件寄存器。从概念上讲,函数调用或中断处理程序总是从它自己的私有UCX 寄存器集合开始执行。被中断或调用函数的 UCX 寄存器不被继承。

在 called function, trap handler,interrupt handler 中,只有 A[10](SP)、A[11](RA)、PSW、PCXI 和D[15] 寄存器(在Trap 场景下) 会从架构定义的值开始。called function, trap handler or interrupt handler 在将值写入其中之前,读取任何其他 UCX 寄存器操作都是未定义的。

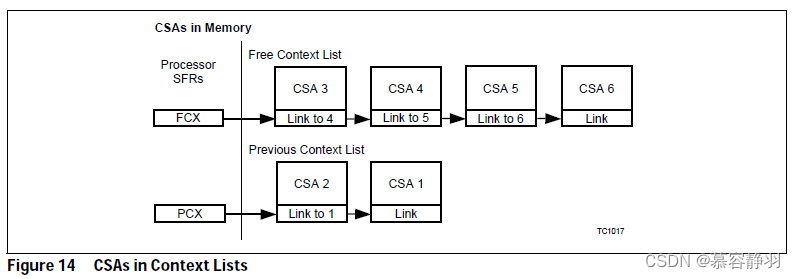

CSAs and Context List

Upper Context 和 Lower Context 都被保存在CSA中,其中:

- 未使用的 CSA 链接在一起,形成一个链表,称为 FCX(Free Context List,自由上下文链表)。其中 FCX 的首地址保存在 FCX 寄存器 中。即 FCX 寄存器的内容始终指向FCX中的可用 CSA。 CSA Link Word 指向自由上下文链表中的下一个可用 CSA。;

- 已经使用的CSA链接在一起,形成一个链表,称为 PCX(Previous Context List)。

在将 UCX 或者 LCX 保存进第一个可用的 CSA 之前,会先读取可用 CSA 中的链接字,作为 FCX的新值。对于内存子系统,上下文保存因此是一个读/修改/写(read/modify/write)操作。FCX的新值指向下一个可用 CSA ,可立即用于后续的UCX、LCX保存。

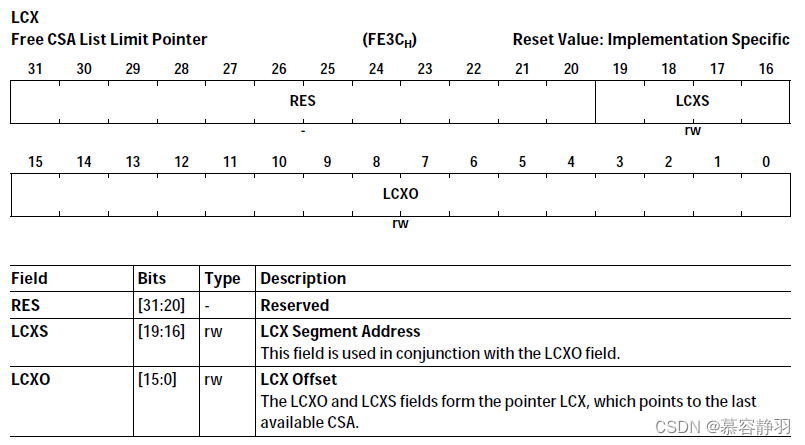

LCX 寄存器 指向 FCX 中最后某个可用 CSA(TC397代码实现中是指向倒数第3个),用作检测CSA链表耗尽。如果在保存 context 的时候 FCX 和 LCX 的值匹配,则当save context 完成后执行下一条指令时就会触发 FCD Trap。( 即,FCD Trap 的返回地址是陷阱/中断/调用例程的第一条指令或 SVLCX 或 BISR 指令之后的指令。)

Trap Handler 采取的行动取决于软件实现。例如,如果确定 CSA 列表耗尽是由不可恢复的软件错误引起的,它可能会发出系统重置。然而,通常它通过分配额外的内存或通过终止一个或多个任务并回收它们的 CSA 调用链来扩展空闲列表。在这些情况下,陷阱处理程序以 RFE 指令退出。

为了支持 FCU Trap,FCX 中最后一个 CSA 中的Link Word 在首次使用之前必须设置为NULL。

为了支持 CSU Trap(调用栈下溢):首次使用 CSA 之前,PCX 指针值应为NULL。

PCXI.PCX 字段指向先前保存上下文的 CSA。 PCXI.UL 标识保存的上下文是Upper (PCXI.UL == 1) 还是Lower (PCXI.UL == 0)。如果该类型与 restore context 的类型不匹配,则会发生 CYTP Exception 并产生 Class3 Trap,且在 Save context 操作完成后会更新 A[11](RA):

- 对于函数调用(CALL),会将函数返回地址写入 A[11](RA)。

- 对于同步陷阱(synchronous trap),将引发 trap 的指令的 PC写入A[11](RA);

- 对于 SYSCALL 和异步陷阱或中断(asynchronous trap or an interrupt),会将下一条要执行的指令的 PC写入A[11](RA) 。

当保存 LCX 时,A[11](RA) 的值包含在已经保存的上下文中,并放置在 CSA 的第二个字中。该 A[11](RA) 相应地由LCX restore 操作来恢复。

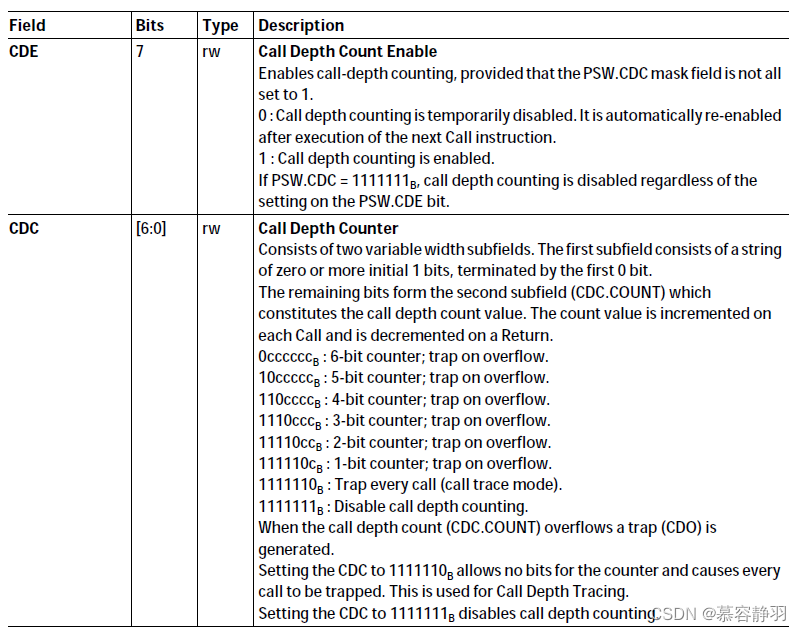

调用深度控制字段(PSW.CDC)由两个子字段组成:

- 调用深度计数器(call depth counter,CDC);

- 确定计数器宽度和溢出时间的掩码( a mask that determines the width of the counter and when it overflows);

CDC 在 call 时递增,并在 return 时恢复到其先前的值。计数器溢出时发生 Exception。其目的是防止软件错误导致 “递归失控(runaway recursion)” 并耗尽CSA

Context Switching with Interrupts and Traps

当Interrupt或者Trap发生的时候,CPU会自动保存当前任务的 UCX到内存中,挂起当前任务,开始启动 ISR或 TSR(Trap Service Handler)。如果处理器未使用中断栈(PSW.IS == 0),则栈指针将加载 ISP 的当前内容。 然后设置 PSW.IS =1,以指示从中断栈执行。

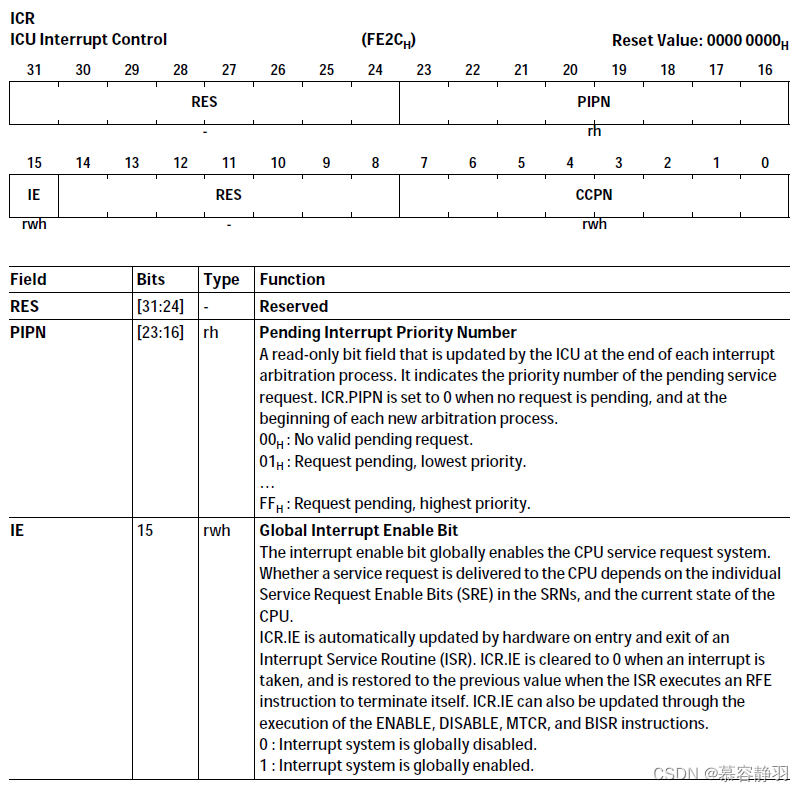

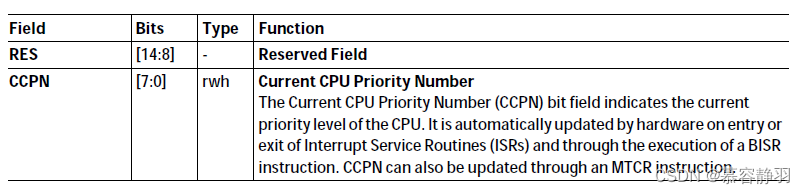

中断管理系统的组成包括:

- ICR( Interrupt Control Register)

- ICR.CCPN :holds the Current CPU Priority Number;

- ICR.IE :the Interrupt Enable bit;

- ICR.PIPN:Pending Interrupt Priority Number.

- PCXI(Previous Context Register)

- PCXI.PCPN:Previous CPU Priority;

- PCXI.PIE:Previous Interrupt Enable;

ICR.CCPN 通常仅在 ISR 中是非零值。

PCXI.PIE 通常仅在 ISR 中触发的 Trap Handler 中为零,比如在外设服务请求期间发生的 NMI 或 SYSTRAP。

对于中断和陷阱,当前 PCXI 中的 PCPN 和 PIE 值都保存在 UCX 的 CSA 中,而 ICR 中 IE 和 CCPN 值被复制到 PCXI.PIE 和 PCXI.PCPN 字段中。一旦处理了中断或陷阱,则在必要时重新加载保存的LCX,并恢复被中断任务的执行 (RFE)。

在中断或陷阱上,当前任务上下文的UCX 由硬件保存。 对于完全可以在保存的这组寄存器中执行的小型中断和陷阱处理程序,不需要进一步的上下文保存。 处理程序可以立即执行并返回。 通常,进行调用或需要更多寄存器的处理程序会执行 BISR(开始中断服务程序)或 SVLCX(保存下层上下文)指令来保存 LCX 寄存器。 该指令必须在任何相关寄存器被修改之前发出,但它不必是处理程序中的第一条指令。

具有关键响应时间要求的中断处理程序可以使用UCX寄存器立即执行其初始的、时间关键的处理。 之后,他们可以执行 BISR 并继续进行时间要求较低的处理。 BISR 重新启用中断,因此使用它可以将时间关键与不太关键的处理分开。

陷阱处理程序通常没有关键的响应时间要求,但是那些可能发生在 ISR 中或可能延迟中断太长时间的程序也可以采用类似的方法来区分不可中断和可中断的执行段。

Context Switching with Function Call

在函数调用中,整个UCX寄存器集由硬件保存。 此外,通过 CALL 指令保存UCX与调用跳转(call jump)并行发生。 此外,恢复 UCX 由 RET(返回)指令执行,并与返回跳转(return jump)并行进行。 被调用函数不需要保存和恢复调用者的上下文,并且不需要限制其对UCX寄存器的使用。 调用函数和被调用函数必须在LCX寄存器的使用上协作。

Fast Function Calls with FCALL/FRET

FCALL 指令执行调用跳转,并将当前返回地址 (A11) 并行保存到栈中, 且不保存其他状态,不保存UCX寄存器。 因此,被调用函数从调用者的上下文开始执行(A10 和 A11 除外)。

FRET 执行用作从 FCALL 返回。FRET 会跳转到当前的返回地址 (A11) 并从栈中加载前一个 A11, 且不加载其他状态。

Context Save and Restore Example

Context Save

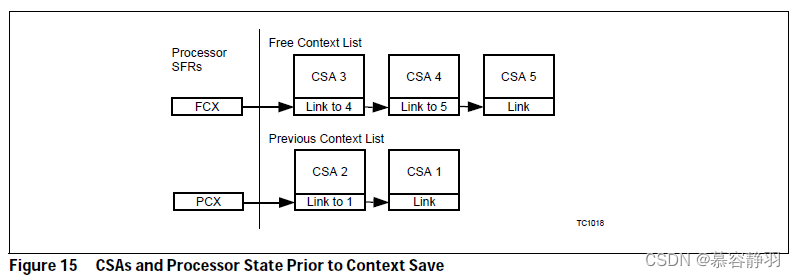

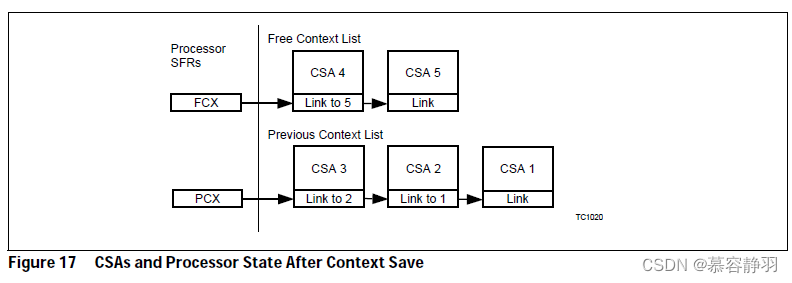

如Figure15所示,CPU 中:

- FCX 寄存器指向 FCX List(包含3个CSA:3,4,5) 的首地址;

- PCX 寄存器指向 PCX List(包含2个CSA:1,2) 的首地址;

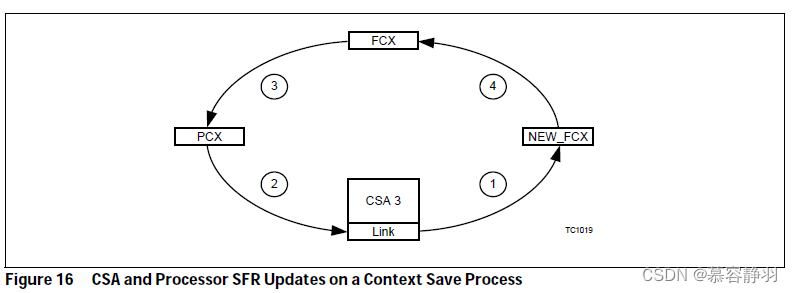

现在要执行 save context 操作,则 Figure15 中 FCX List 中的第一个可用 CSA3 被拉出来并放置在 PCX List 中。具体步骤为(Link Word 简称为 LW):

- 将CSA3 Link Word 中的内容保存到 NEW_FCX 中,现在 NEW_FCX 指向 CSA4。其中, NEW_FCX 是一个内部 buffer,用户不可访问;

- 将PCX的内容写到 CSA3.LW 中,CSA3 现在指向 CSA2;

- 将FCX中的内容写入PCX,PCX现在指向 CSA3。

- 将NEW_FCX的内容加载到FCX中;

即:

FCX_NEW = CSA3.LW; // CSA3.LW 中保存 CSA4 的首地址 CSA3.LW = PCX; // 将 CSA3 由 FCX List 移动到 PCX List PCX = FCX; // 更新 PCXList 的首地址 FCX = FCX_NEW;// 更新 FCX List 的首地址以上操作完成后,两个新的链表如 Figure17 所示:

Context Restore

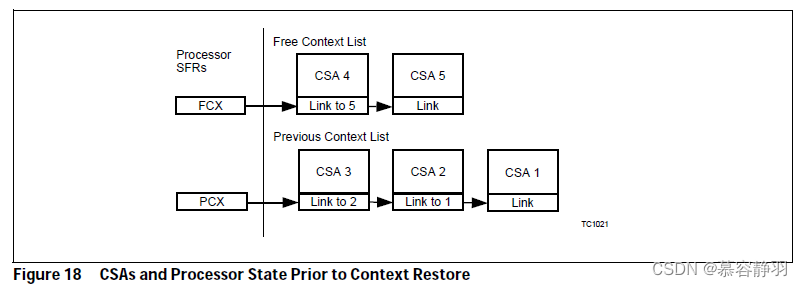

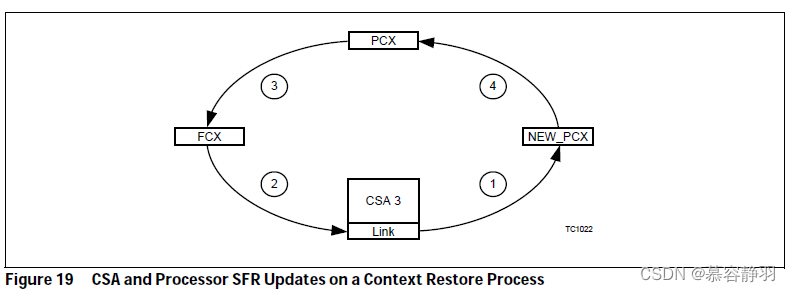

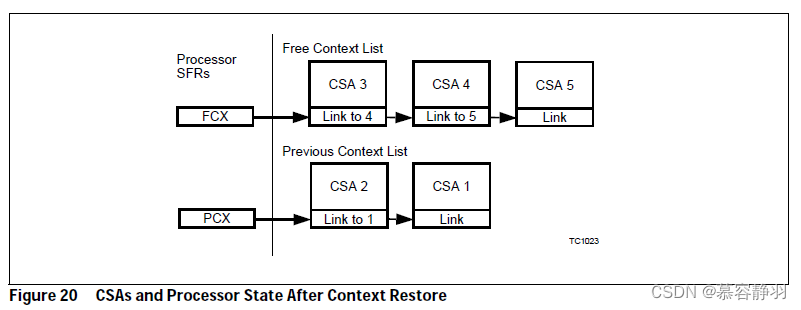

如Figure18 所示,现在要执行 restore context 操作,则 PCX List 中的第一个 CSA3 被拉出来并放置到 FCX List 中。具体步骤为(Link Word 简称为 LW):

- 将CSA3 Link Word 中的内容保存到 NEW_PCX 中,现在 NEW_PCX 指向 CSA2。其中, NEW_FCX 是一个内部 buffer,用户不可访问;

- 将FCX的内容写到 CSA3.LW 中,CSA3 现在指向 CSA4;

- 将PCX中的内容写入FCX,FCX现在指向 CSA3。

- 将NEW_PCX的内容加载到PCX中;

PCX_NEW = CSA3.LW; // CSA3.LW 中保存 CSA2 的首地址 CSA3.LW = FCX; // 将 CSA3 由 PCX List 移动到 FCX List FCX = PCX; // 更新 FCXList 的首地址 PCX = PCX_NEW;// 更新 PCX List 的首地址以上操作完成后,两个新的链表如 Figure20 所示:

Context Management Registers

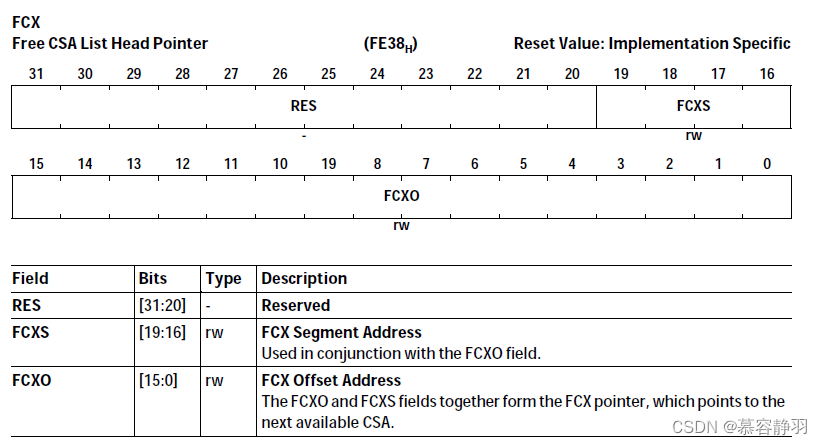

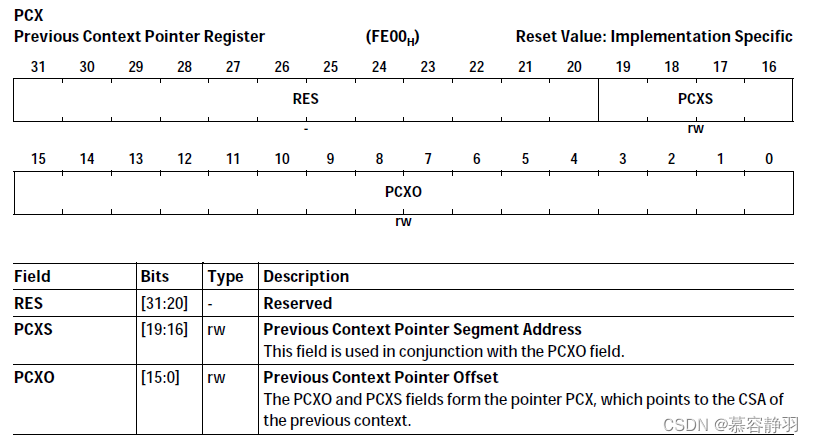

3个管理上下文的寄存器:

- FCX: Free CSA List Head Pointer

- PCX: Previous Context Pointer

- LCX: Free CSA List Limit Pointer

Each pointer consists of two fields:

• A16-bit offset.

• A 4-bit segment specifier.

使用寄存器的两个字段(segment , offset)产生 CSA 的有效地址:

FCX

PCX

LCX

4. Interrupt System

名词列表

类型 | 简称 | 全称 | 说明 |

名词缩写 | ISR | Interrupt Service Routine | 中断服务例程,处理中断的 Func 的简称 |

名词缩写 | SRN | Service Request Node | 服务请求节点 |

名词缩写 | IVT | Interrupt Vector Table | 中断向量表 |

寄存器 | ICR | Interrupt Control Register | 中断控制寄存器 |

ICR 的寄存器位 | IE | Global Interrupt EnableDisable Bit | 标识全局中断是否启用 |

ICR 的寄存器位 | PIE | Previous Global Interrupt Enable Bit | 先前全局中断使能位 |

ICR 名词缩写 | CCPN | Current CPU Priority Number | 当前CPU的优先级编号 |

名词缩写 | PCPN | Previous CPU Priority Number | 先前CPU优先级编号 |

ICR 的寄存器位 + 名词缩写 | PIPN | Pending Interrupt Priority Number | 挂起的中断优先级编号 |

名词缩写 | SRPN 或 IRPN | Interrupt Service Request Priority Number | 中断请求优先级编号 |

硬件单元 | ICU | Interrupt Control Unit | 中断控制单元 |

指令 | ENABLE | Enable interrupt | 启用中断 |

指令 | DISAPBE | Disable Interrupt | 禁用中断 |

指令 | BISR | Begin Interrupt Service Routine | 开始 ISR,作用包括:

|

指令 | MTCR | Move To Core Register | 修改寄存器的值,但是必须紧跟其后使用 ISYNC 指令 |

指令 | MFCR | Move From Core Register | |

指令 | ISYNC | SYNChronize instruction stream | |

指令 | RFE | Return From Exception | |

指令 | RET | Return From Call | |

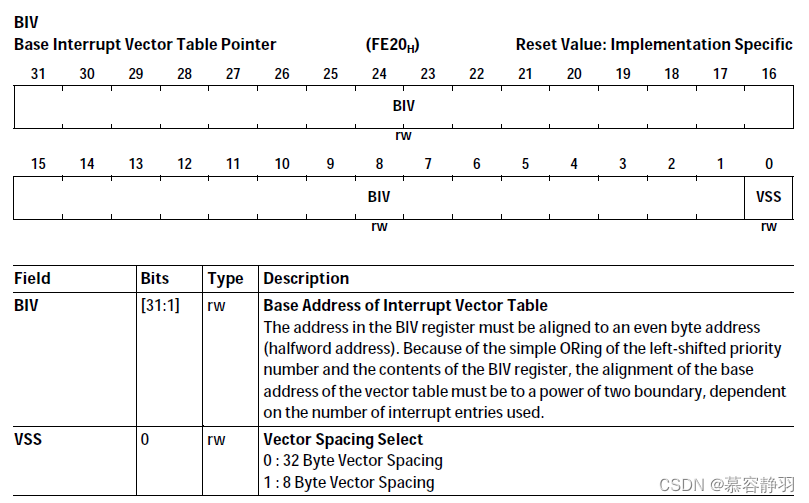

寄存器 | BIV | Base of Interrupt Vector Table register | |

BIV 寄存器位 | VSS | Vector Size Select | |

寄存器 | PC | Program Counter | 程序计数器 |

中断相关操作

General Operation

TODO

每个中断源都被分配一个唯一的 SRPN。 在接收到来自中断源的中断请求时,中断控制单元 (ICU) 使用 SRPN 来决定在多个并发中断请求中优先处理哪一个。获胜的中断请求的 SRPN 与请求触发器一起作为 PIPN 提供给 CPU。CPU 通过将 PIPN 与其当前 CPU的 优先级编号 (CCPN) 进行比较来决定是否接受该中断请求(如果 PIPN > CCPN,接受中断请求)。 如果 CPU 决定接受该中断请求,它会进行中断确认(Interrupt Acknowledge)并返回所接受中断的优先级编号。 然后 ICU 将清除请求的中断源。

SRPN 的取值范围是 [0, 255]。

CPU operation on an interrupt request

CPU 会检查 ICR.IE 的状态,并将 ICR.CCPN 和 PIPN 做比较。只有当同时满足:

- ICR.IE == 1;

- ICR.CCPN < PIPN;

这2个条件时,CPU才会被中断,进入ISR。

PIPN 用来决定中断向量表的入口点(entry point)并通知 ICU,ICU 反过来将确认发送回待处理的中断请求。

以下几种情况可能会阻止 CPU 立即响应 ICU 生成的中断请求:

- The interrupt system is globally disabled (ICR.IE == 0). —— 中断全局禁用;

- The current CPU priority (CCPN), is equal to or higher than the Pending Interrupt Priority Number (PIPN). —— CCPN >= PIPN;

- The CPU is in the process of entering an interrupt or trap service routine.——CPU已经进入ISR 或 TSR;

- The CPU is operating on non-interruptible trap services. —— CPU正在操作不可中断的 Trap Service;

- The CPU is executing a multi-cycle instruction.—— CPU正在执行多周期指令;

- The CPU is executing an instruction which modifies the ICR.—— CPU 正在执行修改ICR的指令;

Entering an Interrupt Service Routine (ISR)

- • The upper context of the current task is saved.

- • The Return Address (A[11]) is updated with the current PC.

- • If the processor was not previously using the interrupt stack (PSW.IS = 0), then the A[10] Stack Pointer is set to the interrupt stack pointer (ISP). The stack pointer bit is then set for using the interrupt stack: PSW.IS = 1.

- • The I/O mode is set to Supervisor mode, which means all permissions are enabled: PSW.IO = 10B.

- • The current Protection Register Set is set to 0: PSW.PRS = 000B.

- • The Call Depth Counter (PSW.CDC) is cleared, and the call depth limit selector is set for 64: PSW.CDC = 0000000B.

- • Call Depth Counter is enabled, PSW.CDE = 1.

- • PSW Safety bit is set to value defined in the SYSCON register. PSW.S = SYSCON.IS.

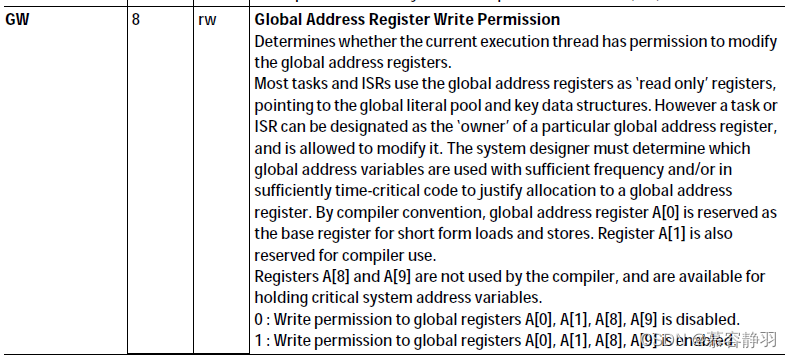

- • Write permission to global registers A[0], A[1], A[8], A[9] is disabled: PSW.GW = 0.

- • The interrupt system is globally disabled: ICR.IE = 0. The old ICR.IE is saved into PCXI.PIE.

- • The Current CPU Priority Number (ICR.CCPN) is saved into the Previous CPU Priority Number (PCXI.PCPN) field.

- • The Pending Interrupt Priority Number (ICR.PIPN) is saved into the Current CPU Priority Number (ICR.CCPN) field.

- • The interrupt vector table is accessed to fetch the first instruction of the ISR.

中文版

- • 保存当前任务的上层上下文(UCX)。

- • 使用当前的 PC 更新返回地址(A[11]) ,即

A[11] = PC。 - • 如果处理器之前没有使用中断堆栈(PSW.IS = 0),则 A[10] 堆栈指针设置为中断堆栈指针(ISP)。 然后设置堆栈指针位以使用中断堆栈:PSW.IS = 1。

if (PSW.IS == 0) { A[10] = ISP; PSW.IS = 1; }- • I/O 模式设置为Supervisor 模式,启用所有权限,即:

PSW.IO = 10B。 - • 当前保护寄存器集合设置为0,即:

PSW.PRS = 000B。 - • 调用深度计数器 (PSW.CDC) 被清除,呼叫深度限制选择器设置为 64,即:

PSW.CDC = 0000000B。 - • 启用调用深度计数器,即

PSW.CDE = 1。 - • PSW 安全位设置为 SYSCON 寄存器中定义的值,即:

PSW.S = SYSCON.IS。 - • 禁用全局寄存器 A[0]、A[1]、A[8]、A[9] 的写权限,即:

PSW.GW = 0。 - • 全局禁用中断系统:即设置

ICR.IE = 0。旧的 ICR.IE 会保存到 PCXI.PIE,即PCXI.PIE = ICR.IE。 - • 将 ICR.CCPN 保存到 PCXI.PCPN中,即:

PCXI.PCPN = ICR.CCPN。 - • 将 ICR.PIPN 保存 到 ICR.CCPN 中,即:

ICR.CCPN = ICR.PIPN。 - • 访问中断向量表以获取 ISR 的第一条指令。

中断系统使用:

ENABLE或BISR指令启用中断,其中:- ENABLE 指定会设置 ICR.IE = 1 (interrupt systemenabled).

- BISR 指令会:

- 设置 ICR.IE = 1;

- ICR.CCPN = a new value;

- saves the lower context of the interrupted task.

DISALBE指令禁用中断,即:- 设置 ICR.IE = 0;

MTCR指令来修改 ICR.IE 和 ICR.CCPN 的值。

几个指令的区别在于:

ENABLE, BISR, DISABLE 指令执行时都会阻止 CPU 接受中断请求,直到指令完全完成。这避免了流水线副作用,因此可以不使用 ISYNC 指令。但是 MTCR 指令后面必须后跟 ISYNC 指令。

Exiting an Interrupt Service Routine (ISR)

使用 RFE指令退出中断,且硬件会自动 restore Upper Context(UCX)。

UCX 中有 PCXI 寄存器,后者包含 PCPN 和 PIE:

- •PCXI.PCPN is written to ICR.CCPN to set the CPU priority number to the value before interruption.

- • PCXI.PIE is written to ICR.IE to restore the state of this bit.

The interrupted routine then continues.

中文版:

ICR.CCPN = PCXI.PCPN;ICR.IE = PCXI.PIE;

Interrupt Vector Table(IVT)

ISR 通过中断向量表与特定优先级的中断相关联。中断向量表是一个数组,其中包含 ISR 入口点(Entry Point)。 中断向量表存储在内存中。

当 CPU 接受中断时,它会计算中断向量表中与中断优先级(ICR.PIPN )相对应的地址,该地址被加载到PC中,然后 CPU 开始在中断向量表中的该地址处执行指令。 该地址处的代码是所选的 ISR 的开始代码。根据 ISR 的代码大小,中断向量表可能只存储 ISR 的初始部分代码,例如一个跳转指令,该指令将 CPU 引导到内存中其他地方的 ISR 剩余部分。

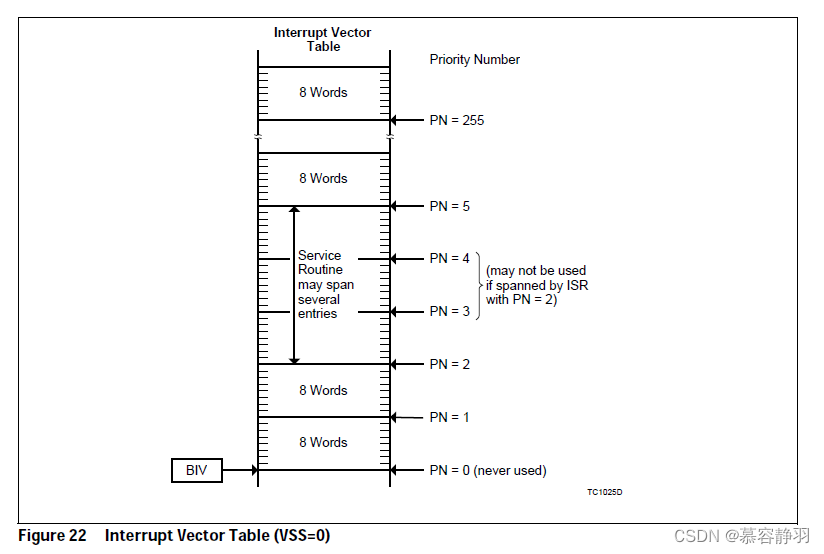

BIV(Base of Interrupt Vector Table Register)寄存器存储中断向量表的起始(基)地址。中断向量在表中按优先级递增排序。BIV 寄存器可以在系统初始化阶段,即启用中断前,(BIV 受 ENDINIT 保护)使用 MTCR 指令进行修改。通过这种方式,系统中可以有多个中断向量表,并通过更改 BIV 寄存器的内容在它们之间进行切换。

中断时,CPU 根据 PIPN 和 BIV 寄存器的内容计算相应ISR的入口点。TriCore 提供两种向量表配置,向量之间的间距为 32 字节到 8 字节。间距由 BIV.VSS 位选择。

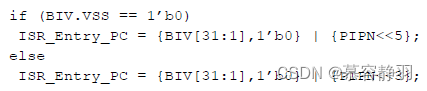

生成指向中断向量表的指针的计算过程:

- PIPN 左移 5 位 (VSS=0) 或 3 位 (VSS=1) ;

- 与 BIV 寄存器中的地址进行或运算以生成指向中断向量表的指针.

ISR 的执行从该地址开始。由于此操作,建议将寄存器 BIV 的位 [14:5] (VSS=0) 或位 [12:3] (VSS=1) 设置为 0。

BIV 寄存器允许中断向量表位于可用代码存储器中的任何位置。 上电时的默认设置取决于具体实现。

如果ISR 很短,可能适合全部存储在向量代码段的内存字中。否则,存储在入口位置的代码可以跨越多个向量入口,或者应该包含一些初始指令,然后跳转到处理程序的剩余部分。

Using the TriCore Interrupt System

Spanning Interrupt Service Routines across Vector Entries

如 Figure22 所示,一个ISR可能在一个 entry(8 words,32 bytes)中放不下,允许跨越几个 entry 放置(比如 PN= 2 的ISR占据了2,3,4三个 entry的位置)。这样做的好处在于可以避免一次Handle 的跳转(相较于在entry中只放置ISR的其实代码和跳转指令)。但是要注意的是,如果一个ISR占据了几个 entry的位置,则被其余占用的entry所对应的优先级编号(如上图中3 和 4)就不能再被分配给SRN,即不能被使用。

使用这种技术会增加给定系统所需的优先级编号范围,但必须相应调整向量表的大小。

Interrupt Priority Groups

中断优先级组合即一组彼此之间不能互相中断的 ISR。

当 CPU 启动中断服务时,中断系统全局禁用,CPU 优先级 CCPN 设置为正在服务的中断的优先级。 从现在开始,CPU不会再处理其他中断,直到通过软件再次启用中断系统,或者使用 RFE(从异常返回)指令终止服务程序。

TODO

Interrupt Control Register

ICR

BIV