【ARMv8/v9 异常模型入门及渐进 9.1 - FIQ 和 IRQ 打开和关闭】

创始人

2024-12-28 20:07:52

0次

请阅读【ARMv8/v9 ARM64 System Exception】

文章目录

- FIQ/IRQ Enable and Disable

- 汇编指令详解

- 功能解释

- 使用场景和注意事项

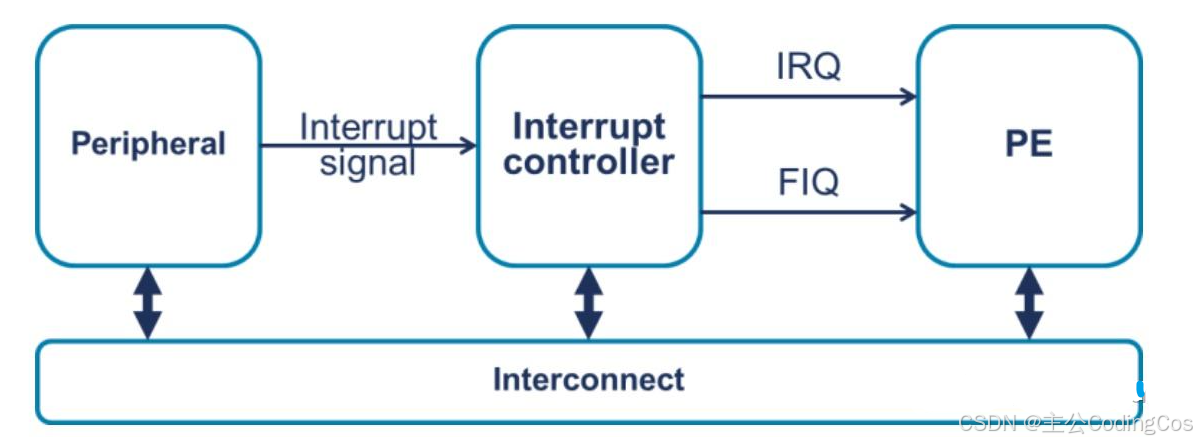

FIQ/IRQ Enable and Disable

在ARMv8/v9架构中,可以使用下面汇编指令来打开FIQ和 IRQ,代码如下:

asm volatile ("msr daifclr, 0x3 \n"); 下面详细介绍这个函数的组成部分和功能:

汇编指令详解

asm关键字用于GCC和一些其他编译器中,表示接下来的字符串是一段内联汇编代码。这允许开发者直接在C或C++代码中嵌入汇编语句。volatile关键字告诉编译器,该汇编代码具有副作用,应当防止编译器优化掉这段代码。在处理器状态控制或硬件相关操作中,volatile通常是必需的,以确保代码按照预期执行。msr daifclr, 0x3是具体的汇编指令:msr(Move to Special Register)是将一个值移动到一个特殊寄存器的指令。daifclr是目标特殊寄存器,代表中断掩码寄存器中的"Disable AIF clear"部分,用于控制处理器的中断使能状态。DAIF是一个位字段,分别代表Debug异常、SMC调用异常、IRQ(普通中断)、FIQ(快速中断)。

0x3指的是要写入daifclr寄存器的值,具体含义是清除(使能)中断。在这里,二进制11(十六进制的0x3)指的是要清除(即使能)IRQ和FIQ中断的禁用状态。具体来说:- 位0 (

0x1) 控制FIQ中断的禁用位。 - 位1 (

0x2) 控制IRQ中断的禁用位。 - 因此,

0x3(0b11) 表示同时使能FIQ和IRQ中断。

- 位0 (

也可对FIQ和 IRQ 进行单独控制,代码如下:

.set DAIF_WR_FIQ_BIT, (1 << 0) .set DAIF_WR_IRQ_BIT, (1 << 1) .set DAIF_WR_ABORT_BIT, (1 << 2) .set DAIF_WR_DEBUG_BIT, (1 << 3) func enable_irq msr daifclr, #DAIF_WR_IRQ_BIT isb ret endfunc enable_irq func disable_irq msr daifset, #DAIF_WR_IRQ_BIT isb ret endfunc disable_irq func enable_fiq msr daifclr, #DAIF_WR_FIQ_BIT isb ret endfunc enable_fiq func disable_fiq msr daifset, #DAIF_WR_FIQ_BIT isb ret endfunc disable_fiq 功能解释

asm volatile ("msr daifclr, 0x3 \n");指令的功能是使能IRQ和FIQ中断,确保处理器能够响应这两种类型的中断请求。在嵌入式或操作系统开发中,运行该指令通常意味着你想要在特定的执行点允许处理器开始响应外部或快速中断,这是一种常见的操作,特别是在初始化或关键操作执行前后需要确保中断系统处于正确状态。

使用场景和注意事项

- 使用场景:内核代码、驱动开发、系统底层控制、中断管理等。

- 注意事项:

- 在使用此类操作时,需要确保对系统的中断机制有充分理解。

- 修改中断掩码状态可能会对系统稳定性和性能产生重大影响,特别是在多任务或实时操作系统中。

- 确保在修改中断掩码前后保存和恢复原有状态,以防止意外禁用重要中断。

通过直接操作特殊寄存器控制中断使能,开发者可以精确控制系统行为,但这也要求高度的谨慎和对平台细节的深入了解。

相关内容

热门资讯

四分钟了解!万能透视辅助器免费...

四分钟了解!万能透视辅助器免费版!一直是有辅助工具(有挂辅助)-哔哩哔哩1、操作简单,无需万能透视辅...

第1分钟了解!天天微友助手破解...

您好,天天微友助手破解版这款游戏可以开挂的,确实是有挂的,需要了解加去威信【485275054】很多...

第十分钟了解!方片十三张脚本!...

第十分钟了解!方片十三张脚本!果然有辅助攻略(有挂辅助)-哔哩哔哩1、任何方片十三张脚本透视是真的假...

第9分钟了解!新金龙辅助工具!...

第9分钟了解!新金龙辅助工具!一直有辅助攻略(有挂方法)-哔哩哔哩1、第9分钟了解!新金龙辅助工具!...

第4分钟了解!胡莱三国辅助工具...

第4分钟了解!胡莱三国辅助工具!总是存在有辅助神器(有挂助手)-哔哩哔哩1)胡莱三国辅助工具有没有挂...

第三分钟了解!湖北逍遥卡五星辅...

第三分钟了解!湖北逍遥卡五星辅助!好像一直都是有辅助教程(有挂头条)-哔哩哔哩1、这是跨平台的湖北逍...

八分钟了解!天天互娱软件!本来...

八分钟了解!天天互娱软件!本来有辅助工具(有挂助手)-哔哩哔哩1、点击下载安装,天天互娱软件脚本分类...

4分钟了解!微信江苏小程序游戏...

4分钟了解!微信江苏小程序游戏破解器下载!好像存在有辅助教程(有挂教学)-哔哩哔哩1、超多福利:超高...

5分钟了解!小闲南川手游辅助器...

5分钟了解!小闲南川手游辅助器!其实是真的有辅助工具(有挂功能)-哔哩哔哩运小闲南川手游辅助器辅助工...

2分钟了解!同乡游辅助软件下载...

2分钟了解!同乡游辅助软件下载!真是存在有辅助攻略(确实有挂)-哔哩哔哩1、完成同乡游辅助软件下载有...